Integrated Multi-Color Light Emitting Device Made With Hybrid Crystal Structure

electrical and electronics

Integrated Multi-Color Light Emitting Device Made With Hybrid Crystal Structure (LAR-TOPS-159)

Method to create red, green, and blue LED device structures on single wafer

Overview

NASA Langley Research Center has developed a process methodology for making red, green and blue LED device structures on the same substrate (wafer), which is not possible today using current techniques. Such devices are manufactured individually because of different crystal structures. This innovation is enabled by the prior innovations by NASA Langley Research Center.

The Technology

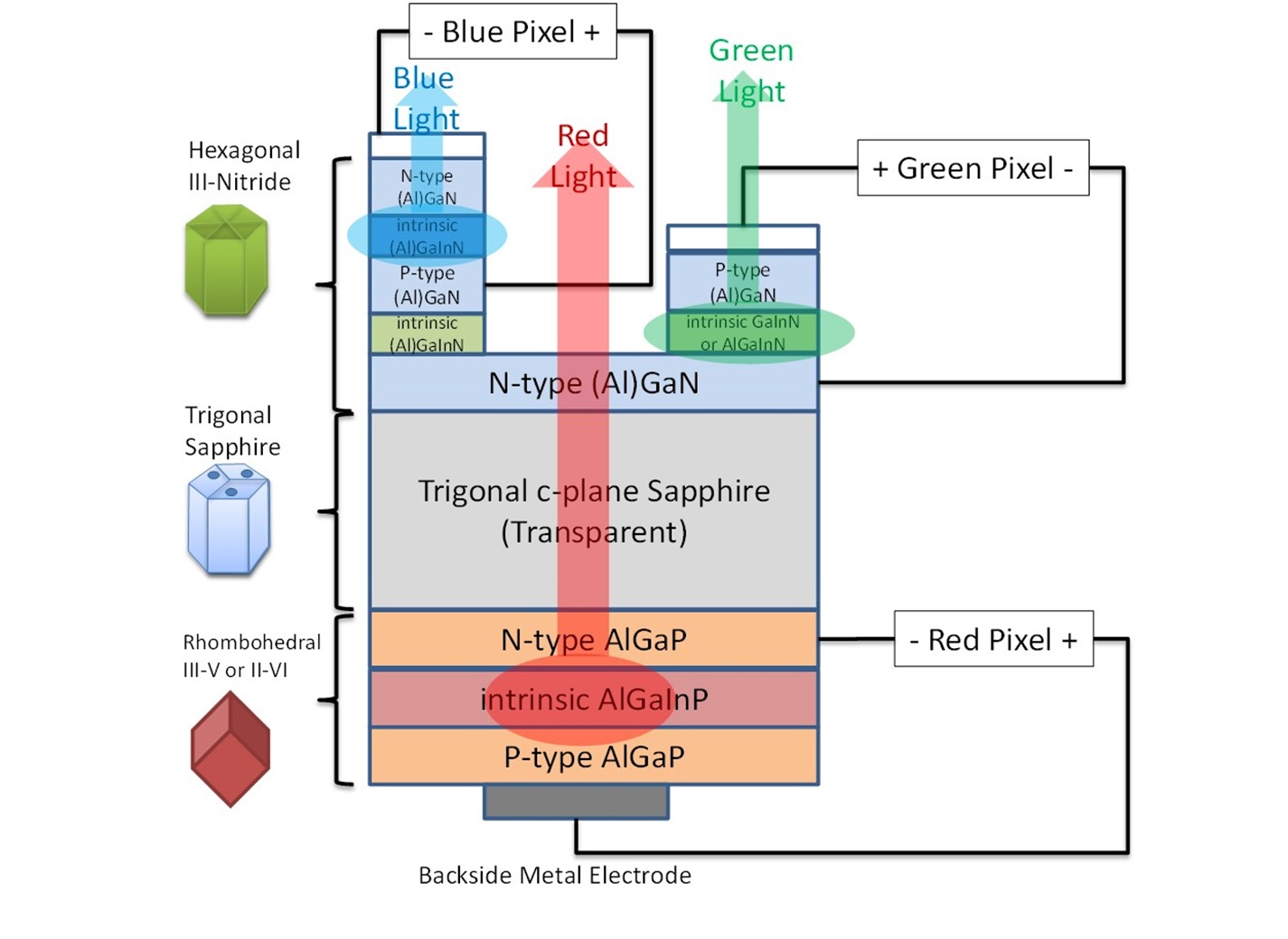

This technology is an integrated hybrid crystal LED display device that can emit red, green, and blue colors on one single wafer. Todays LEDs are built with many compound semiconductors with type-I direct bandgap energies of two different crystal structures. While Red, Orange, Yellow, Yellowish Green LEDs are commonly made with III-V semiconductor alloys of Aluminum Gallium Indium Phosphide (AlGaInP) and Aluminum Gallium Indium Arsenide (AlGaInAs) with cubic zinc blende crystal structures, the higher energy colors such as green, blue, purple, and Ultra-Violet(UV) LEDs are made with III-Nitride compound semiconductor of AlGaInN alloys with hexagonal wurtzite crystal structures. Because the atomic crystal structures are different for red LED and green/blue LEDs, the integration of these semiconductor LEDs as individual R, G, B pixels on one wafer was almost impossible or very difficult so far.

Benefits

- Ability to process red, green and blue LED devices on the same substrate

- LED display and lighting is a significant market opportunity.

Applications

- LED displays

- LED televisions

Similar Results

Double Sided Si(Ge)/Sapphire/III-Nitride Hybrid Structures

III-nitride devices are commonly made on sapphire substrates today for various commercial electronic and optoelectronic applications. Thus, this innovation relates directly to the combination of devices on opposite sides of the sapphire substrate. One possible device combination is to have LEDs one side and solar cells on the other, such as for displays.

Reduced PIC fabrication cost by one-step method

The new fabrication method is an electron lithography scheme enabling monolithic integration of multiple photonic devices on a single PIC. The technology was demonstrated by integrating both a widely-tunable distributed Bragg reflector (DBR) and distributed feedback (DFB) lasers on the same substrate. By controlling the central gap width and etch depth along the laser mirror length (shown in the figure below) the reflectivities can be tuned and the desired laser characteristics can be achieved without additional lithography cycles.

Initially demonstrated on an indium phosphide substrate with DBR and DFB elements, the platform technology shows promise for various other materials and devices like III-V and II-VI semiconductors, silicon-on-insulator (SOI), and planar lightwave circuits (PLCs). With this versatility, the invention described here can streamline PIC production across diverse applications.

Proof-of-concept results showcase the lithographic technique’s ability to produce high-performance photonic devices with side-mode suppression ratios over 50 dB (figure on the right) and output powers exceeding 5 mW. These metrics, combined with the lithographic simplicity, highlight the technology’s potential to reduce costs and accelerate PIC manufacturing. Please note that NASA does not manufacture products itself for commercial scale.

Robotic Assembly of Photovoltaic Arrays

NASA researchers have developed the PAPA technology to increase the efficiency of the thin-film solar array assembly process, significantly decreasing assembly time and labor costs associated with manufacturing large scale solar arrays. Traditional solar cell assembly is a labor intensive, multi-step, time-consuming process. This manual assembly will not be possible in a space environment. To enable solar array assembly in space, PAPA leverages robotic automation to distill the traditional assembly method into four fully automated steps: applying adhesive to block substrate, placing the solar cells using a vacuum tool attached to a universal robotic arm, printing the interconnects and buses to connect the cells, and applying a protective cover.

The PAPA technology is compatible with a variety of thin-film solar cells, including 3D printed cells (essential for future in-space manufacturing of arrays) and terrestrial manufacturing methods. As solar cell technologies mature, PAPA will be able to incorporate advancements into the paneling process. NASA researchers have begun to employ PAPA solar array fabrication and estimate savings of $300-$400/watt. For extraterrestrial assembly of solar panels the size of a football field or larger, PAPA could result in savings of approximately $500 million; a substantial cost savings driven by standardization and efficiency in the solar array assembly process. By demonstrating increases in assembly efficiency, time and cost savings, and passing multiple environmental exposure tests, the PAPA lab protype has completed the final phases of technology development and is ready for scale-up and commercialization.

High-Efficiency Solar Cell

This NASA Glenn innovation is a novel multi-junction photovoltaic cell constructed using selenium as a bonding material sandwiched between a thin film multi-junction wafer and a silicon substrate wafer, enabling higher efficiencies. A multi-junction photovoltaic cell differs from a single junction cell in that it has multiple sub-cells (p-n junctions) and can convert more of the sun's energy into electricity as the light passes through each layer. To further improve the efficiencies, this cell has three junctions, where the top wafer is made from high solar energy absorbing materials that form a two-junction cell made from the III-V semiconductor family, and the bottom substrate remains as a simple silicon wafer. The selenium interlayer is applied between the top and bottom wafers, then pressure annealed at 221°C (the melting temperature of selenium), then cooled. The selenium interlayer acts as a connective layer between the top cell that absorbs the short-wavelength light and the bottom silicon-based cell that absorbs the longer wavelengths. The three-junction solar cell manufactured using selenium as the transparent interlayer has a higher efficiency, converting more than twice the energy into electricity than traditional cells. To obtain even higher efficiencies of over 40%, both the top and bottom layers can be multi-junction solar cells with the selenium layer sandwiched in between. The resultant high performance multi-junction photovoltaic cell with the selenium interlayer provides more power per unit area while utilizing a low-cost silicon-based substrate. This unprecedented combination of increased efficiency and cost savings has considerable commercial potential.

This is an early-stage technology requiring additional development. Glenn welcomes co-development opportunities.

Epitaxy of SiGe and Other Compound Semiconductors

Several of the patented methods included in this suite of technologies enable super-hetero-epitaxy of rhombohedral/cubic compound semiconductors on specially oriented trigonal (e.g. sapphire) or hexagonal (e.g. quartz) crystal wafer substrates. This includes alignment of the growth crystal lattice with the underlying substrate lattice to minimize misfit strain-induced dislocation defects in the growing crystal. Thus thicker, defect-free crystal layers can be made. Rhombohedral/Cubic crystal twin defects which is 60 degree rotated on [111] orientation in a rhombohedral/cubic SiGe layer structure can be reduced to well less than 1% by volume, essentially providing a defect-free semiconductor material. Alternately, engineered lattice structures with a high degree of twinning can provide SiGe with improved thermoelectric properties due to the phonon scattering that inhibits thermal conduction without compromising electrical conductivity. Additional patented technologies in this suite provide for physical vapor deposition (PVD) growth methods utilizing molten sputtering targets and thermal control of heated substrates, including electron beam heating, in order to give the atoms in the sputtered vapor or on the substrate surface the energy needed for the desired crystal growth.

The remaining patented technologies enable x-ray diffraction methods for detecting and mapping crystal twin defects across the entire as-grown semiconductor layer. These defects are critical to the performance of any semiconductor device manufactured from such compound semiconductor materials.